Vi mạch có ở khắp mọi nơi trong thế giới hiện đại. Chúng là trái tim của mọi thiết bị công nghệ mà bạn có thể tưởng tượng. Các công ty công nghệ ngày càng bắt đầu tập trung nhiều hơn vào System-on-Chips (SoC), kết hợp tất cả các chức năng của một thiết bị vào cùng một con chip. Chúng là yếu tố then chốt trong sự phát triển công nghệ và có thể làm tăng đáng kể khả năng cạnh tranh của công ty. Bằng cách phát triển SoC của riêng mình, các công ty có thể kiểm soát toàn bộ lộ trình của mình từ silicon đến web và tạo sự khác biệt bằng cách cung cấp kiến thức chuyên môn chính cho chính họ. Tất cả các công ty công nghệ hàng đầu thế giới đều có sự phát triển công nghệ SoC nội bộ của riêng mình.

Phát triển hệ thống trên chip là một lĩnh vực rất đặc biệt cần thành thạo. Khi cần giải quyết những thách thức quan trọng trong ngành, không ai có thể thực hiện một mình: điều này đòi hỏi sự hợp tác toàn cầu của các công ty và tổ chức nghiên cứu. Cả hai đều cần những tài năng mới và tư duy mới để thành công trong thế giới tương lai.

Tiềm năng đột phá của công nghệ SoC

Công nghệ hệ thống trên chip là nền tảng cho quá trình chuyển đổi kỹ thuật số của EU. Các đối thủ cạnh tranh chính của Châu Âu trong lĩnh vực sản xuất chip là Châu Á và Hoa Kỳ, nhưng Châu Âu hiện đang đẩy mạnh đáng kể hoạt động của mình nhằm nâng cao chủ quyền công nghệ của lục địa này. Đạo luật Chips của EU là sáng kiến mới nhằm tăng năng lực sản xuất chip của châu Âu từ 10% lên 20% thị trường thế giới vào năm 2030. Các công ty sản xuất vi mạch và EU sẽ đầu tư hơn 43 tỷ euro để hỗ trợ Đạo luật Chips.

Sự phát triển SoC cũng liên quan đến địa chính trị. SoC rất quan trọng đối với chuỗi cung ứng. Do đó, việc nâng cao kỹ năng trong lĩnh vực SoC sẽ tăng cường tính bảo mật và giảm sự phụ thuộc vào các quốc gia khác. SoC cũng có tiềm năng tăng cường bảo mật dữ liệu.

Xây dựng chuyên môn của bạn về thiết kế SoC tại Đại học Tampere

Xem xét sự phát triển của ngành và thế giới ngày nay sẽ đi về đâu, có thể nói rằng nhu cầu ngày càng tăng đối với các chuyên gia thiết kế Hệ thống trên Chip trong lĩnh vực công nghệ. Nhu cầu bây giờ đã rất cao. Các chuyên gia vi mạch chuyên thiết kế SoC có rất nhiều giá trị trên thị trường việc làm ngày nay và các công ty luôn mong muốn tuyển dụng tất cả các ứng viên giỏi, cho dù họ mới bắt đầu sự nghiệp hay những chuyên gia giàu kinh nghiệm hơn. Nếu bạn giỏi những gì mình làm và quan trọng nhất là ham học hỏi và thực sự quan tâm, thì cơ hội để bạn phát triển sự nghiệp thăng hoa trong lĩnh vực phát triển SoC là rất cao.

Đại học Tampere có sự kết hợp độc đáo giữa các lĩnh vực chuyên môn bao trùm toàn bộ quá trình phát triển SoC từ silicon đến chip. Ngoài chuyên môn học thuật và các khóa học đa dạng, Đại học Tampere còn có kinh nghiệm trong hợp tác giữa doanh nghiệp và học viện và có mối quan hệ với nhiều công ty cũng như các nhà cung cấp công nghệ lớn trong ngành. Tampere có lịch sử lâu đời và bí quyết vững chắc trong lĩnh vực thiết kế SoC và Đại học Tampere dẫn đầu dự án đồng sáng tạo thiết kế Hệ thống trên Chip tiên phong SoC Hubtrong đó trường đại học làm việc cùng với các công ty địa phương. Khi xem xét tất cả các khía cạnh này, chuyên môn về thiết kế SoC tại Đại học Tampere cho phép bạn có được cái nhìn toàn diện về ngành SoC.

Các nghiên cứu thiết kế Hệ thống trên Chip tại Đại học Tampere bao gồm tất cả các lĩnh vực chuyên môn cần thiết. Điều quan trọng nhất là thiết kế kỹ thuật số vì tất cả các dự án SoC đều liên quan đến nó. Kỹ năng kỹ thuật phần mềm là cần thiết để thực hiện thiết kế kỹ thuật số hiện đại, bởi vì “HW” được thể hiện bằng Ngôn ngữ mô tả phần cứng (HDL) và quá trình này liên quan đến rất nhiều tập lệnh. Các lĩnh vực chuyên môn hỗ trợ là hệ thống nhúng, mạch tương tự và vi điện tử, cần thiết cho các khối xây dựng nền tảng như đồng hồ tốc độ cao và kết nối ngoài chip cấp gigabit. Tuy nhiên, những khối đặc biệt như vậy thường được tái sử dụng và không cần thiết kế mới trong dự án mới. Điện tử, sản xuất và thử nghiệm là bắt buộc vì hầu hết các chip đều cần Bảng mạch in (PCB) để thử nghiệm cũng như cơ sở hạ tầng phòng thí nghiệm. Giao tiếp không dây, xử lý tín hiệu và toán học rất hữu ích trong việc đưa kiến thức ứng dụng đáp ứng các yêu cầu của SoC.

Tại Đại học Tampere, bạn có thể tham gia các nghiên cứu liên quan đến thiết kế Hệ thống trên Chip nếu bạn là sinh viên công nghệ thông tin hoặc kỹ thuật điện và nghiên cứu chuyên ngành về hệ thống nhúng. Đầu tiên, chúng ta sẽ xem System-on-Chip là gì và nó được thiết kế như thế nào.

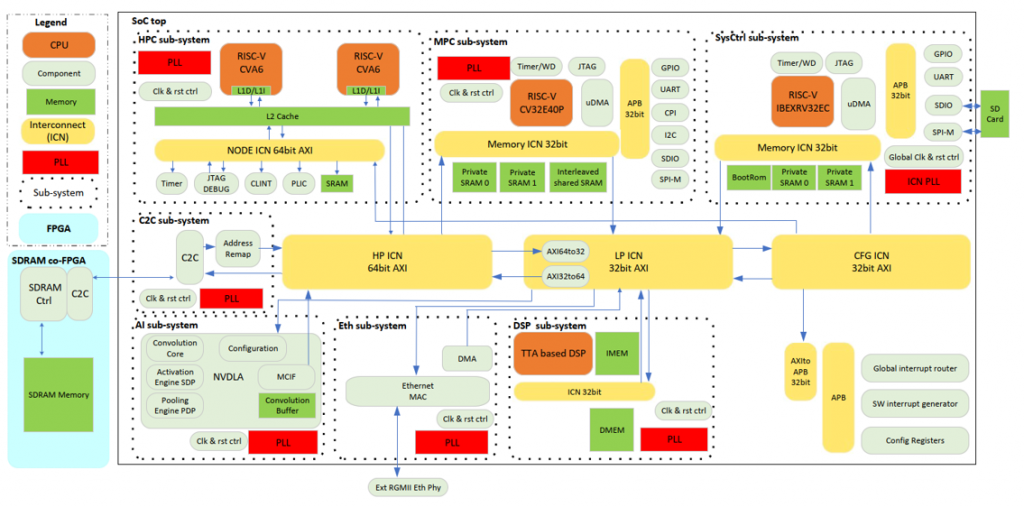

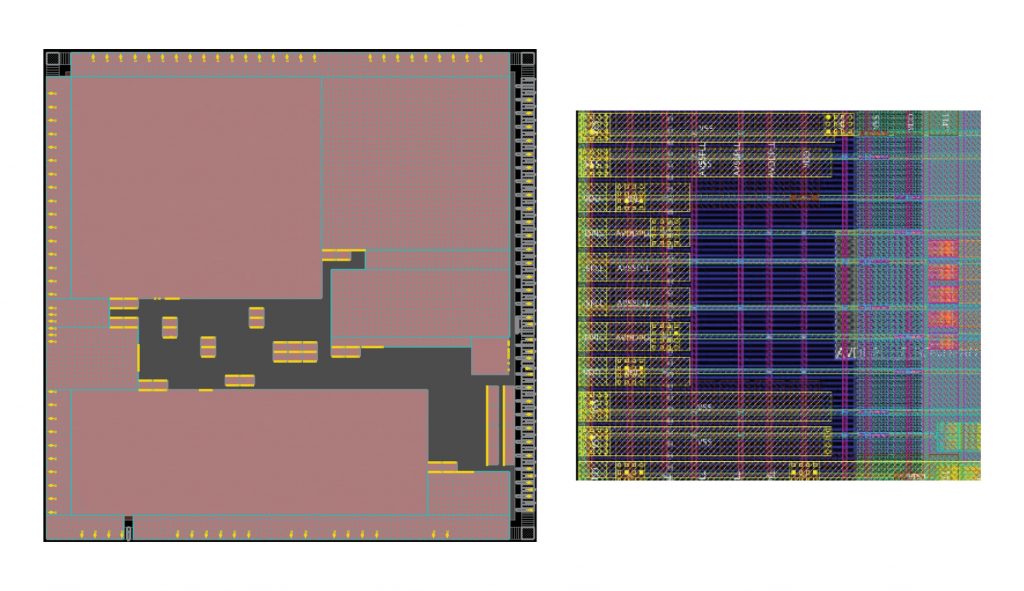

Đúng như tên gọi của nó: một hệ thống được tích hợp trên một con chip duy nhất. Vì ngày càng có thể tích hợp nhiều hơn nên hệ thống bao gồm các hệ thống con, lần lượt bao gồm các Khối Sở hữu Trí tuệ (IP) là các khối xây dựng cơ bản. Lõi bộ xử lý là một khối IP, nhưng với tất cả các bộ nhớ trên chip và các thiết bị ngoại vi, nó tạo thành một hệ thống con bộ xử lý. Ví dụ: chip “Ballast” đầu tiên của SoC Hub bao gồm ba hệ thống con RISC-V, một hệ thống con DSP, một hệ thống con tăng tốc máy học (NVDLA) và một hệ thống con Ethernet. Các hệ thống con được kết nối với nhau thông qua các bus trên chip (AXI) và các giao diện bên ngoài là chip tới chip (C2C) cho các hệ thống khác, Ethernet và các IO ngoại vi khác nhau. Clocking (PLL) được phân phối và hình thành các miền với tốc độ khác nhau.

Sơ đồ kiến trúc của con chip đầu tiên “Ballast” của SoC Hub

Ballast dành cho điện toán IoT/Edge có mục đích chung. Thông thường, chuyên môn về SoC có thể không phù hợp với bất kỳ ứng dụng nào và nhà thiết kế có thể sử dụng các kỹ năng tương tự trong nhiều dự án. Tuy nhiên, các hệ thống con và khối IP có thể được tối ưu hóa cao cho một mục đích cụ thể, điều này cũng đòi hỏi sự hiểu biết về ứng dụng.

Làm cách nào để thiết kế Hệ thống trên Chip?

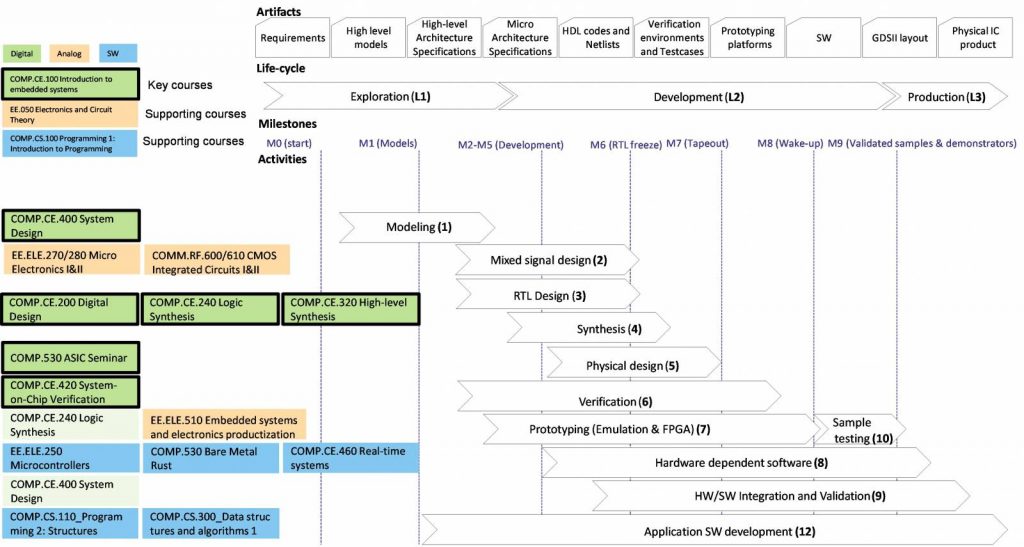

Các giai đoạn chính của quy trình thiết kế Hệ thống trên chip là Thăm dò, Phát triển và Sản xuất theo vòng đời của sản phẩm. Các quyết định lớn nhất được đưa ra trước tiên khi các yêu cầu được đặt ra và tìm hiểu dựa trên các công nghệ, lịch trình và chi phí sẵn có. Sự phát triển bao gồm thiết kế phần cứng và phần mềm cũng như xác minh và tích hợp chúng. Sau khi các mẫu chip được chấp nhận và phần mềm ổn định, việc sản xuất có thể bắt đầu với số lượng lớn. Công việc có tính chất lặp đi lặp lại nhưng nhiều nhiệm vụ phải được thực hiện theo trình tự chặt chẽ trong mỗi giai đoạn.

Sơ đồ cho thấy các khóa học SoC chính của Đại học Tampere có liên quan như thế nào đến quy trình thiết kế SoC

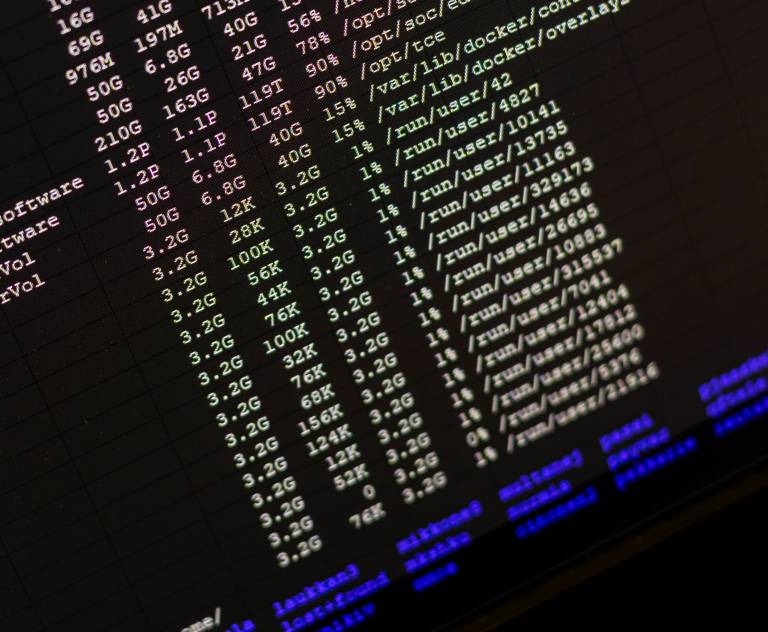

Thiết kế SoC yêu cầu thiết lập dung lượng máy chủ rộng rãi để tính toán và lưu trữ, công cụ thiết kế, tệp thiết kế và kho dữ liệu, quyền truy cập vào thư viện công nghệ ASIC cũng như các phòng thí nghiệm vật lý và thiết bị để kiểm tra chip. Ví dụ: máy chủ SoC Hub có 144 lõi CPU @ 4 GHz và RAM 4,5 TB. Các công cụ thiết kế, thư viện và tệp công việc của chúng tôi tiêu tốn tổng cộng 14 TB ổ đĩa.

Ngoài việc quản lý quy trình thiết kế và chuỗi cung ứng sản xuất, các thỏa thuận pháp lý và quản lý quyền là rất quan trọng. Thông thường, thiết kế yêu cầu khối IP của bên thứ ba, ví dụ như bộ nhớ trên chip sẽ rất tốn công sức để thiết kế từ đầu. Vì lý do này, môi trường thiết kế cũng hỗ trợ tích hợp các khối xây dựng từ các nguồn khác nhau.

Hiện vật

Luồng thiết kế tạo ra các tài liệu, vật liệu, tệp và thiết bị hỗ trợ hữu hình cụ thể mà chúng tôi gọi là tạo phẩm thiết kế. Đối với Khám phá (L1), chúng là các yêu cầu, đặc tả kiến trúc cấp cao, mô hình cấp cao (HLM) và đặc tả kiến trúc vi mô. Các tạo phẩm Phát triển (L2) điển hình bao gồm các mã ngôn ngữ mô tả phần cứng (HDL) được tổng hợp thành các danh sách mạng mô tả mạch mà máy có thể đọc được và cuối cùng là các mô tả bố cục bóng bán dẫn vật lý ở định dạng GDSII để sản xuất chip. Các tạo phẩm hỗ trợ bao gồm các trường hợp thử nghiệm và dữ liệu, môi trường xác minh ảo và thiết kế nền tảng tạo mẫu vật lý, chẳng hạn như trong FPGA. Phần mềm có các tạo phẩm riêng cũng như trao đổi thông tin giữa phần cứng và phần mềm. Giai đoạn sản xuất (L3) bao gồm chính con chip được sản xuất, gói chip, trình độ sản xuất và mẫu chip kiểm tra bảng mạch in hoặc đế ghim của thiết bị đo lường.

Các mốc quan trọng (M0-M9) cho thấy mức độ sẵn sàng của SoC trong quá trình thiết kế. Các mốc quan trọng được sử dụng để đồng bộ hóa công việc giữa các hoạt động phát triển và làm điểm kiểm soát chất lượng.

Giai đoạn Phát triển (L2) bao gồm một số mốc quan trọng (M2-M5) phản ánh sự hoàn thiện về thiết kế từ các mô hình dự thảo chưa hoàn thiện đến các mô hình đã được xác minh. RTL Freeze (M6) có nghĩa là kiến trúc (ví dụ như đầu vào và đầu ra, hệ thống con, khối IP và miền đồng hồ) không thể thay đổi và công việc rất rộng rãi hướng tới Tape-out (M7) bắt đầu. Đây là thời điểm chip đi vào sản xuất vật lý và việc thiết kế CTNH dừng lại. Tape-out là một thuật ngữ lịch sử bắt nguồn từ thời điểm mà lượng lớn dữ liệu thiết kế dành cho sản xuất được truyền bằng băng từ lớn. Sau khi chế tạo, chip được đánh thức (M8), có nghĩa là các chức năng CTNH cơ bản như xung nhịp, đặt lại và khởi động bộ xử lý đang hoạt động. Sau đó, con chip này có thể được bàn giao cho những người trình diễn ứng dụng tập trung vào thử nghiệm và phát triển phần mềm hơn. Tại thời điểm này, chip đã sẵn sàng và nó bao gồm gói hỗ trợ bo mạch (BSP) để phát triển SW cấp thấp và thường là bộ công cụ phát triển phần mềm (SDK) để lập trình ứng dụng.

Trừu tượng

Thiết kế SoC yêu cầu nhiều mức độ trừu tượng của thiết kế. Cấp cao nhất giải quyết chức năng thuần túy trong đó thời gian không được xem xét mà chỉ điều chỉnh dữ liệu và hành vi đầu vào và đầu ra. Thời gian được đưa vào đầu tiên ở độ phân giải thô ở mô hình cấp giao dịch (TLM) và cuối cùng ở mức chính xác của chu kỳ đồng hồ. Sự trừu tượng hóa thời gian càng thấp thì quá trình chạy mô phỏng càng mất nhiều thời gian. Ví dụ: việc khởi động Linux trên mô hình bộ xử lý chính xác theo chu kỳ có thể mất nhiều ngày mô phỏng. Không thể mô phỏng tương tự vào bất kỳ thời điểm hợp lý nào bằng cách sử dụng các mô hình cấp độ bóng bán dẫn. Do đó, mức độ trừu tượng cao hơn được áp dụng để tiết kiệm thời gian và công sức phát triển.

Các khóa học được kết nối với sự phát triển SoC trong đời thực như thế nào?

Đại học Tampere dạy kỹ thuật thiết kế chip trong nhiều khóa học khác nhau. Tiếp theo, chúng tôi sẽ cho biết các khóa học của chúng tôi có liên quan như thế nào đến quy trình thiết kế SoC với sự trợ giúp của các hoạt động được mô tả trong sơ đồ.

Các hoạt động

Công việc thiết kế SoC thực sự được thực hiện trong các hoạt động. Các mũi tên trong sơ đồ luồng thiết kế SoC mô tả thời gian và thứ tự chung cũng như nhiệm vụ chính của từng hoạt động. Trong mỗi hoạt động có hàng chục nhiệm vụ chi tiết.

Các hoạt động phát triển SoC bắt đầu bằng việc lập mô hình, được dạy trong khóa học Thiết kế hệ thống. Mục đích của việc lập mô hình là đưa ra những quyết định đúng đắn vì quy trình tổng thể rất phức tạp và những thay đổi lớn sau đó sẽ tốn kém. Trong giai đoạn này, các yêu cầu đối với hệ thống được xác định và khám phá bằng các mô hình hệ thống trừu tượng trong SystemC có thể được thực thi, mô phỏng và phân tích. Hệ thống này bao gồm một thực thể lớn bao gồm kiến trúc, mô-đun và giao diện cho cả CTNH và SW. Các phần của mô hình hệ thống trừu tượng có thể được tạo ra để triển khai, ví dụ như tự động lấy mã Verilog HDL từ các mô hình IP-XACT.

Dự án Thiết kế Hệ thống bao gồm hàng terabyte dữ liệu

Tiếp theo bắt đầu thiết kế CTNH chi tiết. Điều quan trọng nhất là thiết kế CTNH kỹ thuật số được thực hiện bằng cách viết mã HDL ở mức trừu tượng mức chuyển đăng ký (RTL), tức là thiết kế RTL . Ngoài ra, các tập lệnh được sử dụng để tạo và thao tác cơ sở mã cũng như tích hợp các khối IP từ nhà cung cấp bên thứ ba. Thiết kế RTL giống với lập trình phần mềm hơn nhiều so với thiết kế mạch trong thiết kế tín hiệu hỗn hợp. Cả thiết kế analog và kỹ thuật số đều có thể được thực hiện song song.

Thiết kế tín hiệu hỗn hợp thường được gia công từ các nhà cung cấp IP. Khi thiết kế tín hiệu hỗn hợp được đưa vào dự án, chức năng trên vi điện tử tương tự ở ranh giới của thiết kế CTNH tương tự và kỹ thuật số sẽ được tạo ra. Ví dụ: cần có vòng khóa pha (PLL) để tạo tín hiệu xung nhịp mức GHz bên trong chip hoặc cổng hiển thị HDMI yêu cầu mạch thu phát tốc độ rất cao. Điều này đòi hỏi phải nắm vững thiết kế cấp độ bóng bán dẫn mà bạn sẽ học những điều cơ bản trong các khóa học Vi điện tử I và II và Mạch tích hợp I và II. Việc thiết kế được thực hiện bằng các công cụ tự động hóa thiết kế điện tử (EDA) với sơ đồ mạch vẽ.

Tổng hợp là một nhiệm vụ được tự động hóa cao nhằm tạo ra cấu trúc cấp thấp của cổng, thanh ghi và kết nối cho công nghệ FPGA hoặc ASIC. Các khóa học Thiết kế kỹ thuật số, Tổng hợp logic và Tổng hợp cấp cao (HLS) bao gồm cả thiết kế và tổng hợp RTL. Khóa học Thiết kế Kỹ thuật số đào tạo những kiến thức cơ bản về mạng cổng, máy trạng thái, đơn vị số học và kiến trúc hệ thống kỹ thuật số. Logic Synt tổng hợp đào tạo thiết kế kỹ thuật số bằng ngôn ngữ HDL ở mức độ trừu tượng RTL (VHDL). Đối với các nhà phát triển phần cứng mới, đây là kỹ năng quan trọng nhất và kiến thức trong lĩnh vực này theo truyền thống rất được các công ty đánh giá cao. Hơn nữa, khóa học Tổng hợp cấp cao (HLS) xem xét cách mã cấp độ RTL có thể được tạo tự động từ ngôn ngữ C hoặc C++, giúp tăng năng suất thiết kế.

Vị trí các khối logic trên chip (FPGA) sau khi tổng hợp

Thiết kế vật lý có nghĩa là tạo ra bố cục bóng bán dẫn trên khuôn silicon. Đầu vào của nó là netlist từ giai đoạn tổng hợp và nó tạo ra vị trí và định tuyến của các bóng bán dẫn. Tuy nhiên, người thiết kế thường chỉ nhìn thấy các ô tiêu chuẩn bao gồm các bóng bán dẫn như cổng, thanh ghi, bộ nhớ, kết nối và các khối khác. Chỉ có thiết kế tùy chỉnh hoàn toàn mới hiển thị các bóng bán dẫn đơn cho nhà thiết kế. Khóa hội thảo của chúng tôi về Phần cuối ASIC Kỹ thuật số đề cập đến tất cả các bước cần thiết để thiết kế chip sẵn sàng băng từ.

Ở bên trái, hình ảnh bố cục của chip SoC Hub “Ballast” mô tả cách các khối chức năng được định vị vật lý bên trong chip.

Các miếng đệm IO được liên kết với các chân của gói được hiển thị ở hai bên. Ở bên phải, bố cục chip được phóng to.

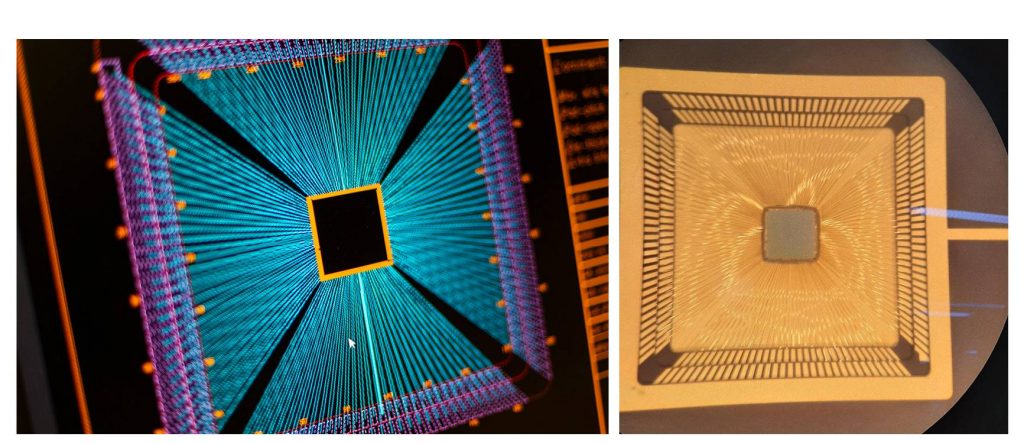

Thiết kế bao bì chip dằn (bên trái) và khâu lắp ráp cuối cùng (bên phải)

Cần có bao bì để gắn khuôn silicon đã sản xuất vào phần còn lại của sản phẩm điện tử giống như bảng mạch in. Thiết kế gói bắt đầu khi bố cục và loại miếng đệm IO được cố định trong thiết kế vật lý. Các nhiệm vụ bao gồm việc lựa chọn loại gói, thiết kế định tuyến nội bộ bên trong gói. Khuôn thường được gắn vào bao bì bằng liên kết dây hoặc trực tiếp bằng bề mặt khuôn gọi là flip-chip.

Xác minh là một quá trình đảm bảo rằng thiết kế SoC đáp ứng thông số kỹ thuật của nó và nó thường được thực hiện dưới dạng mô phỏng. Điều này được dạy trong khóa học Xác minh hệ thống trên chip. Chúng tôi sử dụng tiêu chuẩn Phương pháp xác minh toàn cầu (UVM) làm xương sống, cũng như ngôn ngữ SystemVerilog.

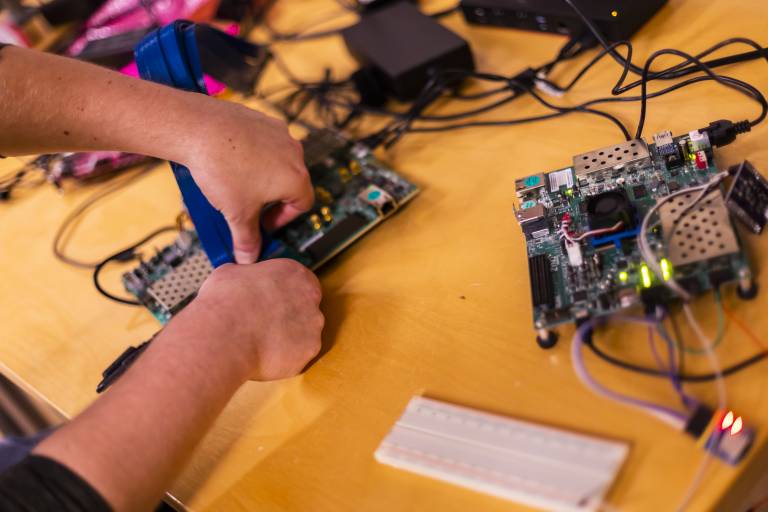

Nguyên mẫu ở đây đề cập đến thử nghiệm vật lý của chip. Trong quá trình tạo mẫu, mô tả RTL của chip được tổng hợp thành FPGA có thể lập trình, sau đó mô phỏng chip. Trọng tâm là chức năng vì thời gian và tốc độ xung nhịp thường khác nhau giữa SoC và FPGA cuối cùng. Nguyên mẫu được đề cập trong nhiều khóa học sử dụng FPGA làm nền tảng bài tập của chúng tôi.

Thiết lập nguyên mẫu FPGA.

Việc kiểm tra mẫu diễn ra khi khuôn được đóng gói được chuyển đến từ nơi sản xuất. Nó bao gồm việc giải nén các con chip, lắp ráp chúng vào một bảng mạch in (PCB) tùy chỉnh và bắt đầu thử nghiệm bằng cách kiểm tra điện. Sau đó, quá trình đánh thức thực sự bắt đầu, trong đó mức năng lượng và đồng hồ được khởi động theo trình tự và việc kiểm tra tất cả các khối và hệ thống con bên trong dựa trên JTAG được thực hiện. Khóa học Sản xuất Hệ thống nhúng và Điện tử của chúng tôi dạy cách tạo PCB.

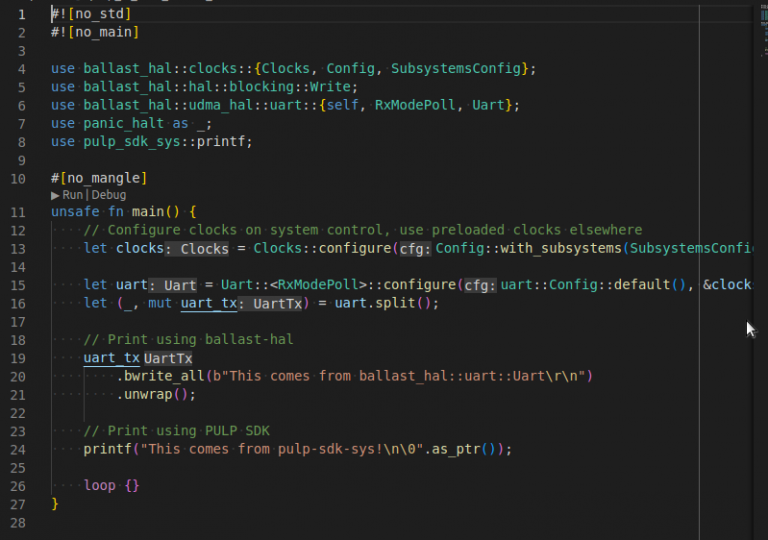

Phần mềm tương tác với phần cứng bằng cách đọc và ghi các thanh ghi CTNH ở mức thấp nhất. Các bản đồ bộ nhớ cần thiết cho SW được tạo từ dữ liệu thiết kế CTNH, ví dụ như các mẫu IP-XACT. Sau đó, cái gọi là phần mềm phụ thuộc vào phần cứng sẽ được tạo ra từ các chi tiết trừu tượng cấp thấp từ người lập trình. Tập hợp các thư viện và chức năng thường được gọi là gói hỗ trợ bo mạch (BSP), do đó cần có bộ công cụ phát triển phần mềm (SDK) dành cho người lập trình ứng dụng. Chúng tôi dạy cách tạo chương trình ngay trên HW trong hội thảo Bare Metal Rust cũng như cách xây dựng Linux và tạo trình điều khiển thiết bị CTNH cụ thể cho Linux trong khóa học Hệ thống thời gian thực của chúng tôi.

Mã để kiểm tra thiết bị ngoại vi CTNH

Một trong những bước cuối cùng trong thiết kế SoC là tích hợp và xác thực CTNH/SW . Khóa học Thiết kế hệ thống bao gồm cả khóa học lập trình và thiết kế kỹ thuật số. Như một bài tập, nó tạo ra một bộ mã hóa video HEVC hoàn chỉnh, trong đó một phần chức năng được thực thi trong bộ xử lý và một phần trong thiết kế CTNH tùy chỉnh trong Linux.

Cuối cùng, khi các mẫu chip được kiểm tra, quá trình chuyển giao từ triển khai CTNH sang phát triển phần mềm ứng dụng diễn ra. Bộ Khóa học Kỹ thuật phần mềm và Phát triển phần mềm mở rộng của chúng tôi được khuyến nghị cho những nhiệm vụ này.

Các khóa học liên quan đến thiết kế SoC tại Đại học Tampere

Khóa học cần thiết

Thiết kế kỹ thuật số:

– COMP.CE.100 Giới thiệu về hệ thống nhúng

– COMP.CE.200 Thiết kế kỹ thuật số

– Tổng hợp logic COMP.CE.240

– Tổng hợp cấp cao COMP.CE.320

– Thiết kế hệ thống COMP.CE.400

– COMP.CE.420 Xác minh hệ thống trên chip

– Khóa học sau đại học về máy tính COMP.530: Hội thảo ASIC

Kỹ thuật máy tính:

– Kiến trúc máy tính COMP.CE.130

Những hệ thống nhúng:

– Vi điều khiển EE.ELE.250

Kỹ thuật phần mềm:

– Lập trình COMP.CS.100 1: Giới thiệu về Lập trình

– COMP.CS.110 Lập trình 2: Cấu trúc

– COMP.CS.300 Cấu trúc dữ liệu và thuật toán 1

– COMP.SE.100 Giới thiệu về Công nghệ phần mềm

– COMP.SE.110 Ohjelmistojen suunnittelu / Thiết kế phần mềm

– COMP.SE.121 Quản lý quy trình và sản phẩm phần mềm

Khóa học hỗ trợ

Vi điện tử:

– Lý thuyết mạch và điện tử EE.050

– Vi mạch điện tử EE.ELE.270 I

– Vi điện tử EE.ELE.280 II

– Mạch tích hợp COMM.RF.600 CMOS I

– Mạch tích hợp COMM.RF.610 CMOS II

– COMM.RF Thiết kế mạch .700 RF

– Đường truyền và ống dẫn sóng COMM.RF.430

Thiết bị điện tử:

– EE.020 Elektroniikan perusteet (FI)

– EE.ELE.210 Transistorit và vahvistinpiirit

– EE.ELE.200 Elektroniikkalaitteen tuotesuunnittelu

– COMM.RF.200 Johdatus RF-elektroniikkaan

– EE.ELE.450 Vật lý thiết bị bán dẫn

– EE.ELE. 510 Sản xuất hệ thống nhúng và điện tử

Kỹ thuật máy tính:

– Số học máy tính COMP.CE.260

– Máy tính song song COMP.CE.350

– Hệ thống thời gian thực COMP.CE.460

– Khóa học sau đại học COMP.530 về máy tính: Rust kim loại trần

– Đồ họa máy tính COMP.CE.430

Những hệ thống nhúng:

– EE.ELE.500 Mikrokontrollerijärjestelmät (FI)

– EE.ELE.510 Hệ thống nhúng và sản xuất điện tử

– EE.ELE.520 Verkotetut sulautetut järjestelmät (FI)

Kỹ thuật phần mềm:

– Đồng thời COMP.CS.310

– Hệ điều hành COMP.CS.410

Toán học:

– MATH.MA.210 Toán rời rạc

– MATH.APP.27 Thuật toán đồ thị

– MATH.APP.460 Phân tích số

– COMP.CS.330 Automata và ngôn ngữ hình thức

– COMP.CS.420 Giới thiệu về đặc tả hình thức

– MATH.MA. 610 Graafiteoria (FI)

Giao tiếp không dây:

– Khóa học cơ bản COMM.100 về Kỹ thuật truyền thông

– Khóa học cơ bản COMM.SYS.200 về truyền thông không dây

– Lý thuyết truyền thông

COMM.SYS.300 – Truyền thông kỹ thuật số

COMM.SYS.400 – Kỹ thuật đa sóng mang và đa anten COMM.SYS.450

– COMM.SYS .700 Truyền thông di động 5G

– Khóa học phòng thí nghiệm hệ thống truyền thông COMM.SYS.800

– Nền tảng vô tuyến được xác định bằng phần mềm COMM.SYS.650

– Khóa học nâng cao COMM.SYS.900 về truyền thông kỹ thuật số

– COMM.SYS.660 Kiến trúc vô tuyến và xử lý tín hiệu

Xử lý tín hiệu:

– COMP.SGN.100 Giới thiệu về Xử lý Tín hiệu

– DATA.ML.100 Giới thiệu về Nhận dạng Mẫu và Học máy

– COMP.SGN.110 Giới thiệu về Xử lý Hình ảnh và Video

– COMP.SGN.200 Xử lý Tín hiệu Nâng cao

Vina Aspire là công ty tư vấn, cung cấp các giải pháp, dịch vụ CNTT, An ninh mạng, bảo mật & an toàn thông tin tại Việt Nam. Đội ngũ của Vina Aspire gồm những chuyên gia, cộng tác viên giỏi, có trình độ, kinh nghiệm và uy tín cùng các nhà đầu tư, đối tác lớn trong và ngoài nước chung tay xây dựng.

Các Doanh nghiệp, tổ chức có nhu cầu liên hệ Công ty Vina Aspire theo thông tin sau:

Email: info@vina-aspire.com | Website: www.vina-aspire.com

Tel: +84 944 004 666 | Fax: +84 28 3535 0668

![]()

Vina Aspire – Vững bảo mật, trọn niềm tin